[Weekly Review] 2020/03/02-08

2020/03/02-08

This week, I worked out the architecture details of Eyeriss V2, and I modified the logic of ProcessingElement, also separated inAct data connections and control logics out of PE Cluster top, making it more clearly and convenient for testing.

Plus, I modified this blog, separated all read papers.

I read two papers as well:

- An efficient kernel transformation architecture for binary- and ternary-weight neural network inference

- Hardware for Machine Learning: Challenges and Opportunities

Chisel

Connection between left (Bool(Wire in PECluster)) and source (Bool(Wire in PECluster)) failed @: Locally unclear whether Left or Right (both internal)

wireVec(i)(j) <> connectedWireVec((i + j + 2) % 3)

I connect wire with <>, so I need to change it with :=.

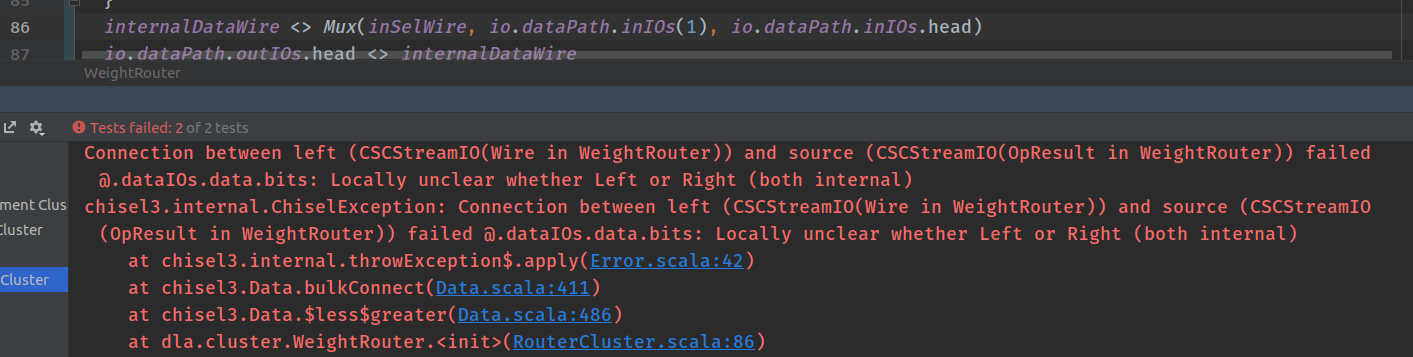

Connection between left (CSCStreamIO(Wire in WeightRouter)) and source (CSCStreamIO(OpResult in WeightRouter)) failed @.dataIOs.data.bits: Locally unclear whether Left or Right (both internal)

internalDataWire <> Mux(inSelWire, io.dataPath.inIOs(1), io.dataPath.inIOs.head)

We can change it with when condition.

when (inSelWire) {

internalDataWire <> io.dataPath.inIOs(1)

} .otherwise {

internalDataWire <> io.dataPath.inIOs.head

}

The MuxLookup should change to when elsewhen otherwise too.

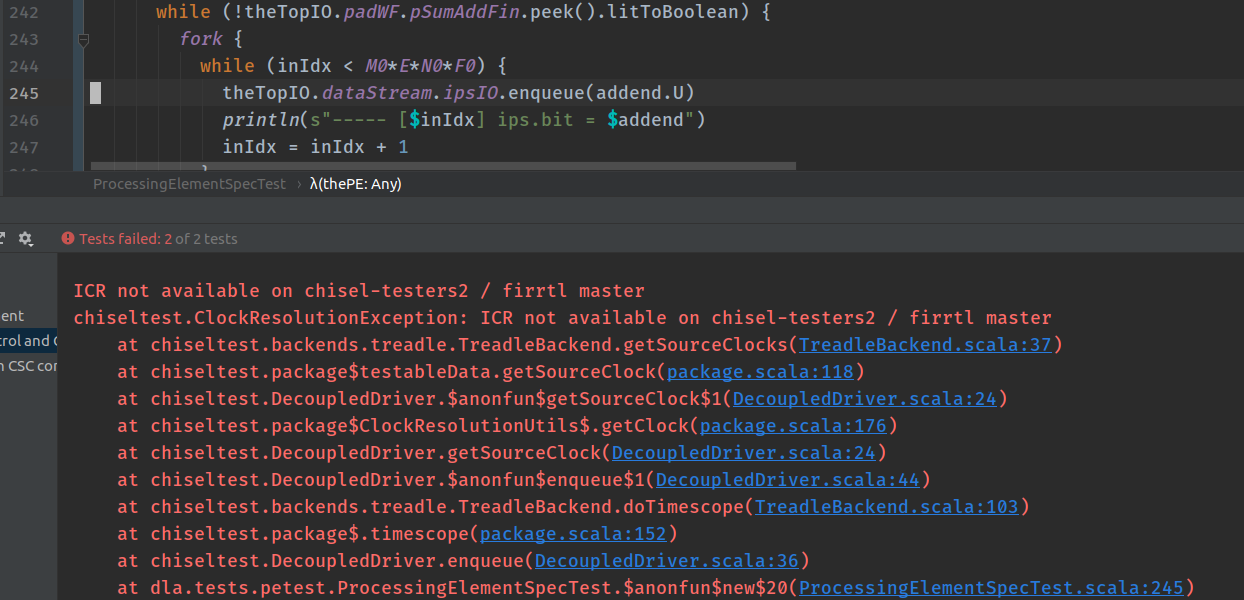

DecoupledDriver

When I used DecoupledDriver.enqueue, I met this error.

We just need to setSourceClock.

theTopIO.dataStream.ipsIO.setSourceClock(theClock)

And setSinkClock is need for ready signal.

Linux

Tree

$singularity:~/chipyard/sims/verilator$ tree -L 2

.

├── generated-src

│ └── example.TestHarness.TinyRocketConfigTest

├── Makefile

├── simulator-example-TinyRocketConfigTest-debug

├── verilator_install

│ ├── install

│ ├── src

│ └── verilator-4.016.tar.gz

└── verilator.mk

5 directories, 4 files

tree -a:

tree -d:

tree -L [number]:

tree -f: