[Emulate] Different Abstraction Models

- Different Abstraction Models

- Specification Model – Functional View

- Component-Assembly Model – Architectural View

- Bus Arbitration Model – Architectural View

- Bus Functional Model – Micro-architectural View

- Cycle-Accurate Computation – Micro-architectural View

- RTL Model – Pure Micro-architecture View

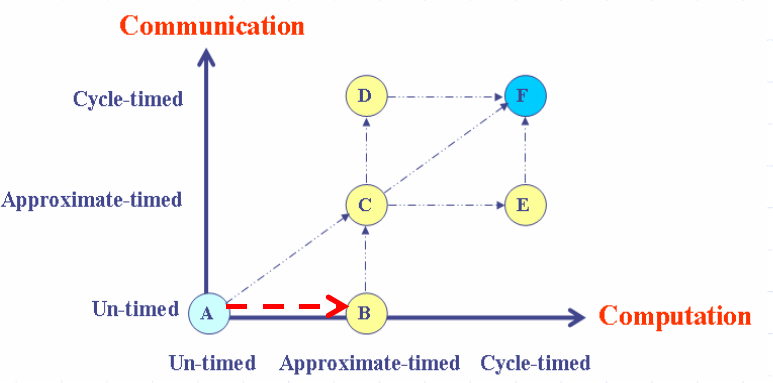

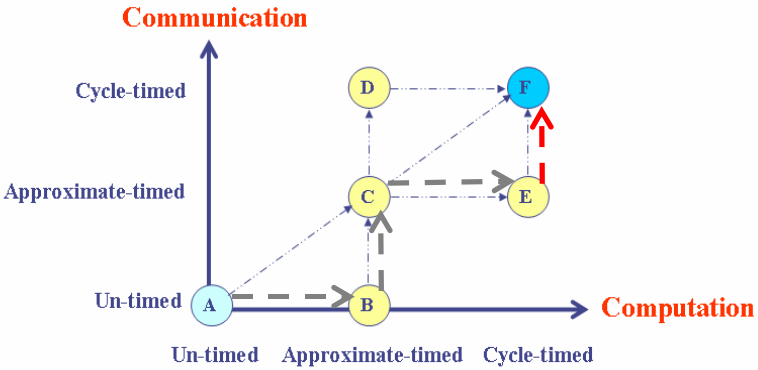

- From Specification to Micro-architecture

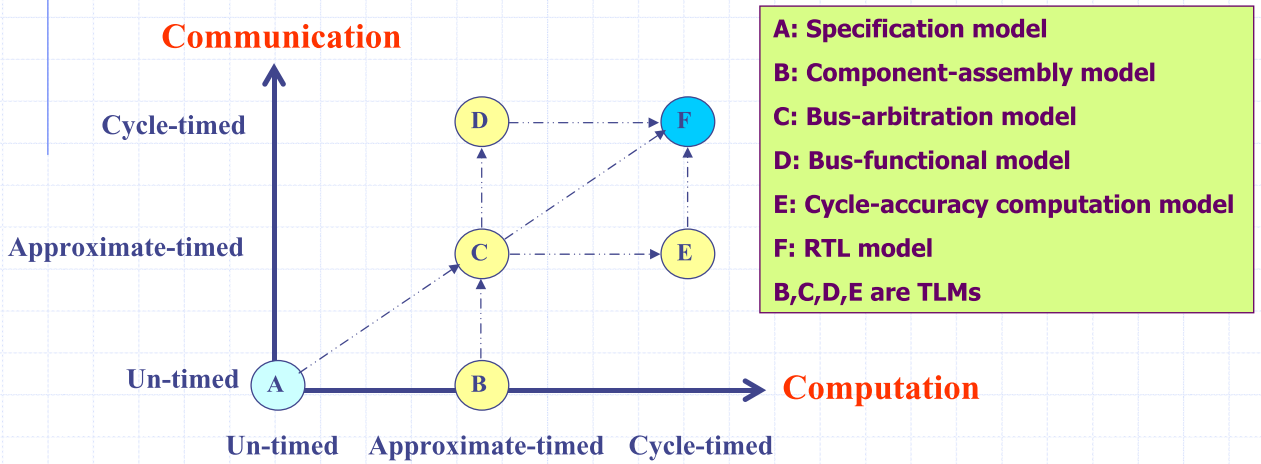

Different Abstraction Models1

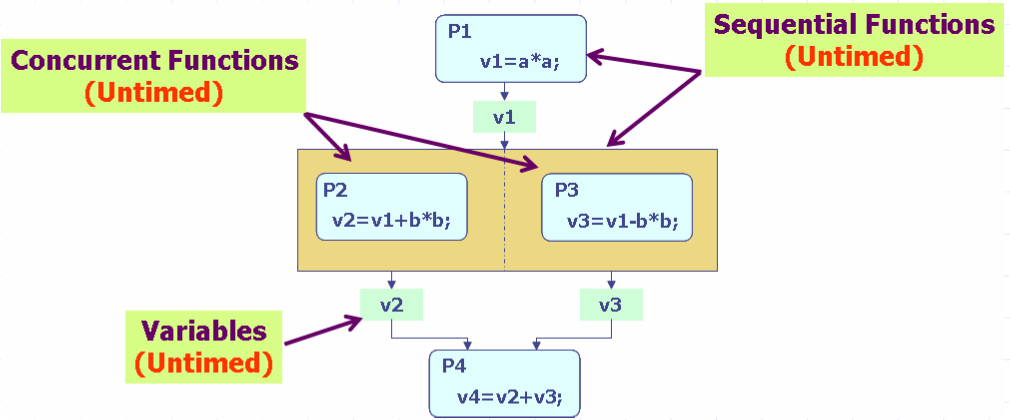

Specification Model – Functional View

- The system functionality without implementation details

- Data transfer is modeled by variable accessing without any concept of channel

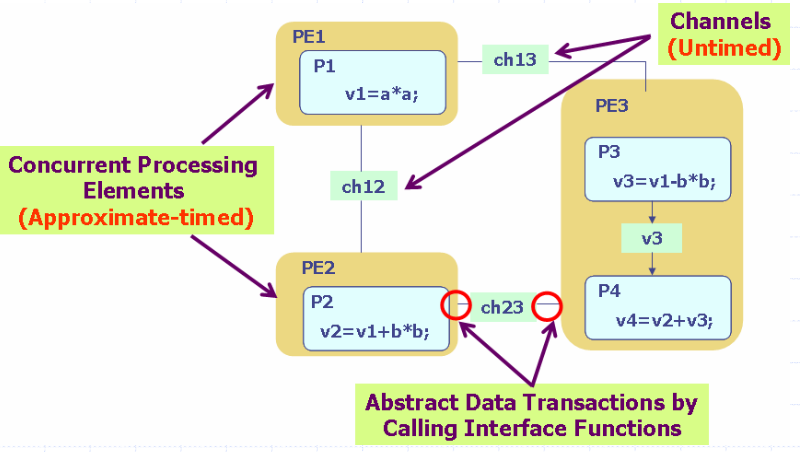

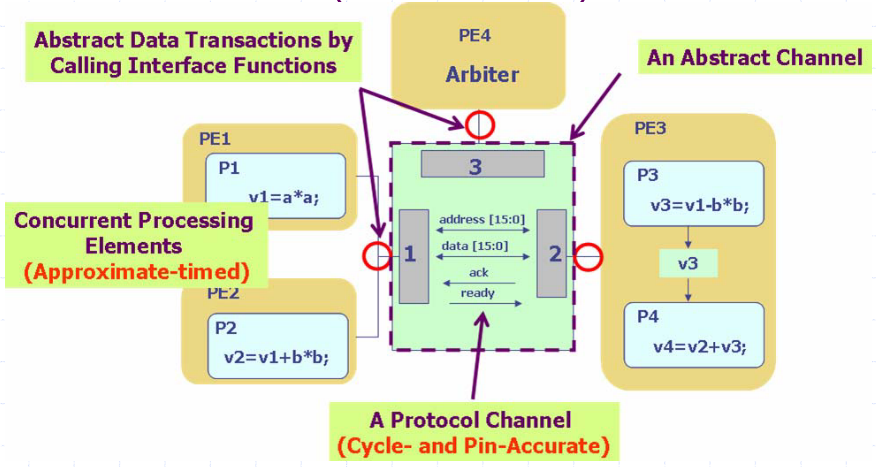

Component-Assembly Model – Architectural View

- Allocation of concurrent processing elements and mapping of processes

- Data transfer is achieved by message passing channels

- Message-passing channels

- An abstract implementation of communication focusing on data transaction

- No cycle-accurate, pin-accurate details, and no specific bus protocol

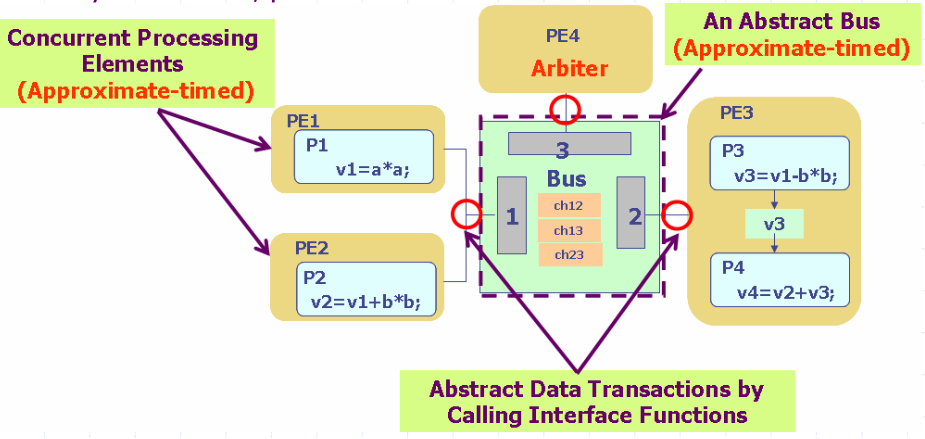

Bus Arbitration Model – Architectural View

- Channels between PEs are realized by an abstract bus

- Require design decision in both computation and communication

- An abstract bus

- Data transfers are still implemented by message passing

- Bus protocol is simplified as blocking and non-blocking I/O

- Arbiter is required to resolve bus conflicts

- No cycle-accurate, pin-accurate details

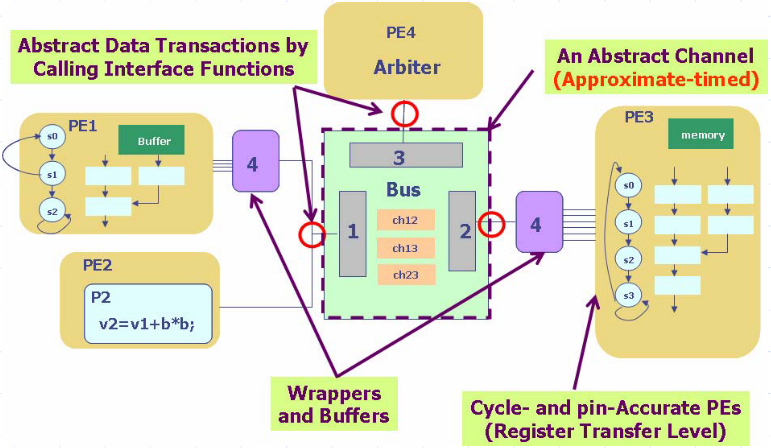

Bus Functional Model – Micro-architectural View

- Abstract bus channel is inline with a cycle-/pin-accurate protocol channel

- Wires of the bus are instantiated with variables/signals

- Data transfer follows the time/cycle-accurate sequence

- Provide interface functions for all abstract bus transactions

- Wrappers convert data transfer from higher level of abstraction (PEs) to lower level of abstraction (Protocol Channel)

Cycle-Accurate Computation – Micro-architectural View

- The PEs are cycle- and pin-accurate

- Dedicated hardware IPs are modeled at register transfer level

- Programmable processors are modeled by instruction set simulator

- Wrappers convert data transfer from higher level of abstraction (abstract bus) to lower level of abstraction (PEs)

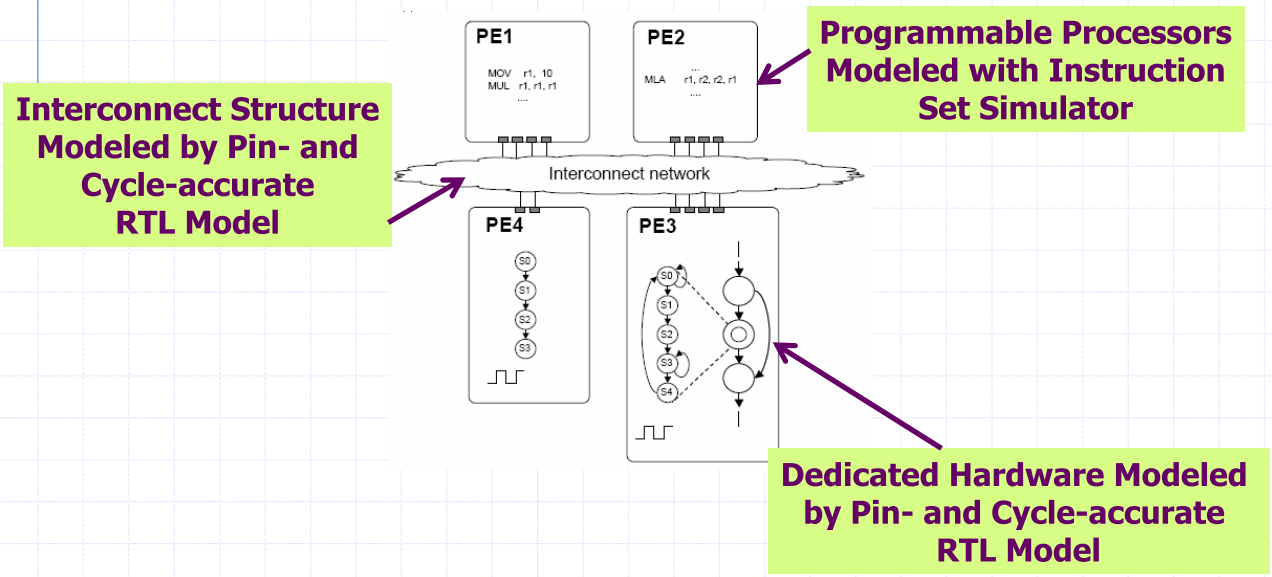

RTL Model – Pure Micro-architecture View

Both computation and communication are pin- and cycle-accurate

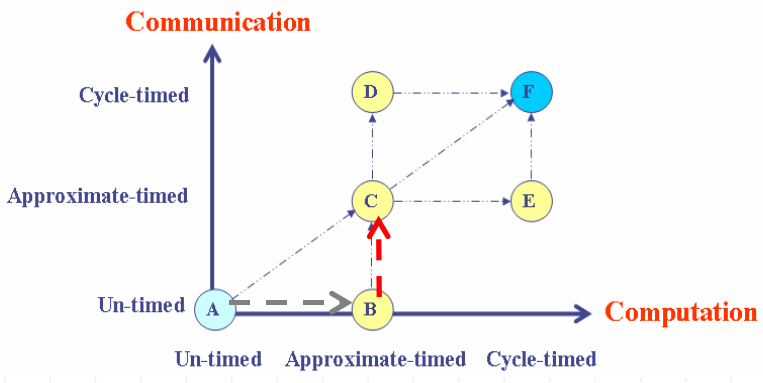

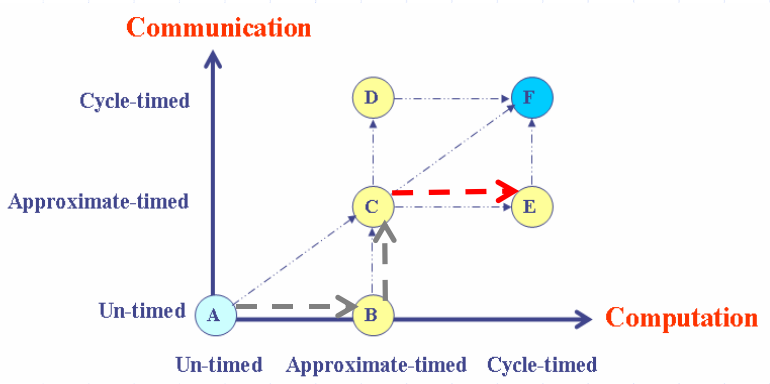

From Specification to Micro-architecture

Component Assembly

- Based on the algorithm analyses, we perform the following tasks

- Partition the algorithm into SW/HW tasks

- Select general purpose CPU or DSP based on the SW characteristics

- Choose RTOS if necessary

- Design IPs or select IPs from library according to the HW tasks

- Define the functionalities of each IP

- Define the interfaces and the data to be exchanged between IPs

- Estimate functional delays in IPs

Communication Exploration

- Decision of interconnect structure

- Back-door connections or centralized buses

- Assign bus-accessing properties for each IP (master or slave)

- Decide the bus arbitration policy

- Estimate functional delays in communication

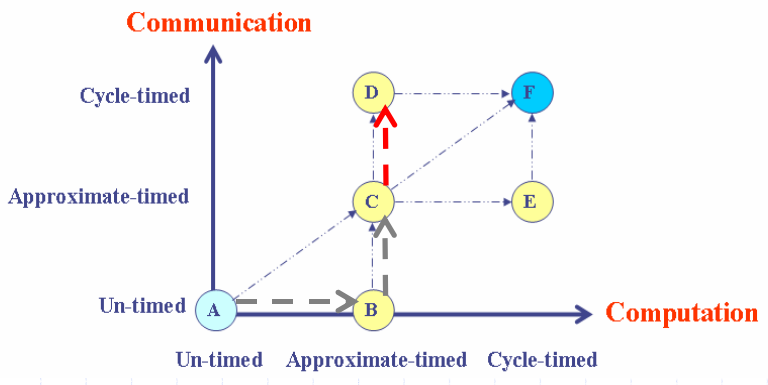

Protocol Refinement

- Inline abstract bus with protocol channel

- Determine the pin- and cycle-accurate bus protocol

- Work out the details of the bus control signals

- Wrappers are used to bridge the models of different abstractions

- Extract delays in communication from micro-architecture

IP Refinement

- The IPs are refined to pin- and cycle-accuracy

- Delays in computation are extracted from micro-architecture

- The embedded SW is optimized to achieve real-time performance

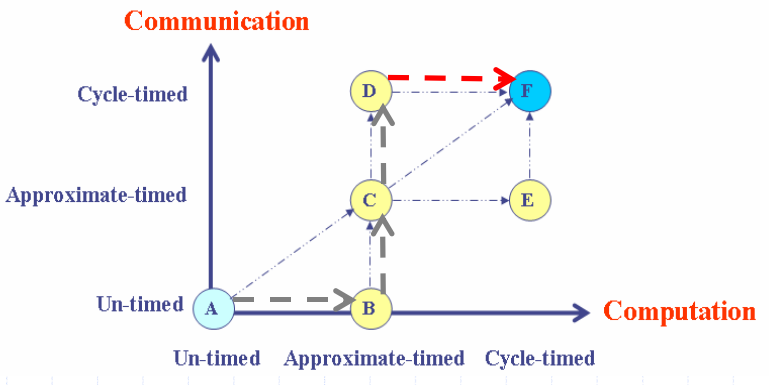

IP Replacement

- Some IPs are modeled with pin- or cycle-accuracy

- The IPs are replaced or refined one by one

- Wrappers are used to bridge the models of different abstractions

Communication Refinement

- Inline abstract bus with protocol channel

- Determine the pin- and cycle-accurate bus protocol

- Work out the details of the bus control signals

- Extract delays in communication from micro-architecture

- Wrappers are used to bridge the models of different abstractions

-

IOC5080(5940) System Model Design and Verification, Department of Computer Science, National Chiao-Tung University ↩