[Glean] VC Formal Apps

VC Formal Apps1

Introduction

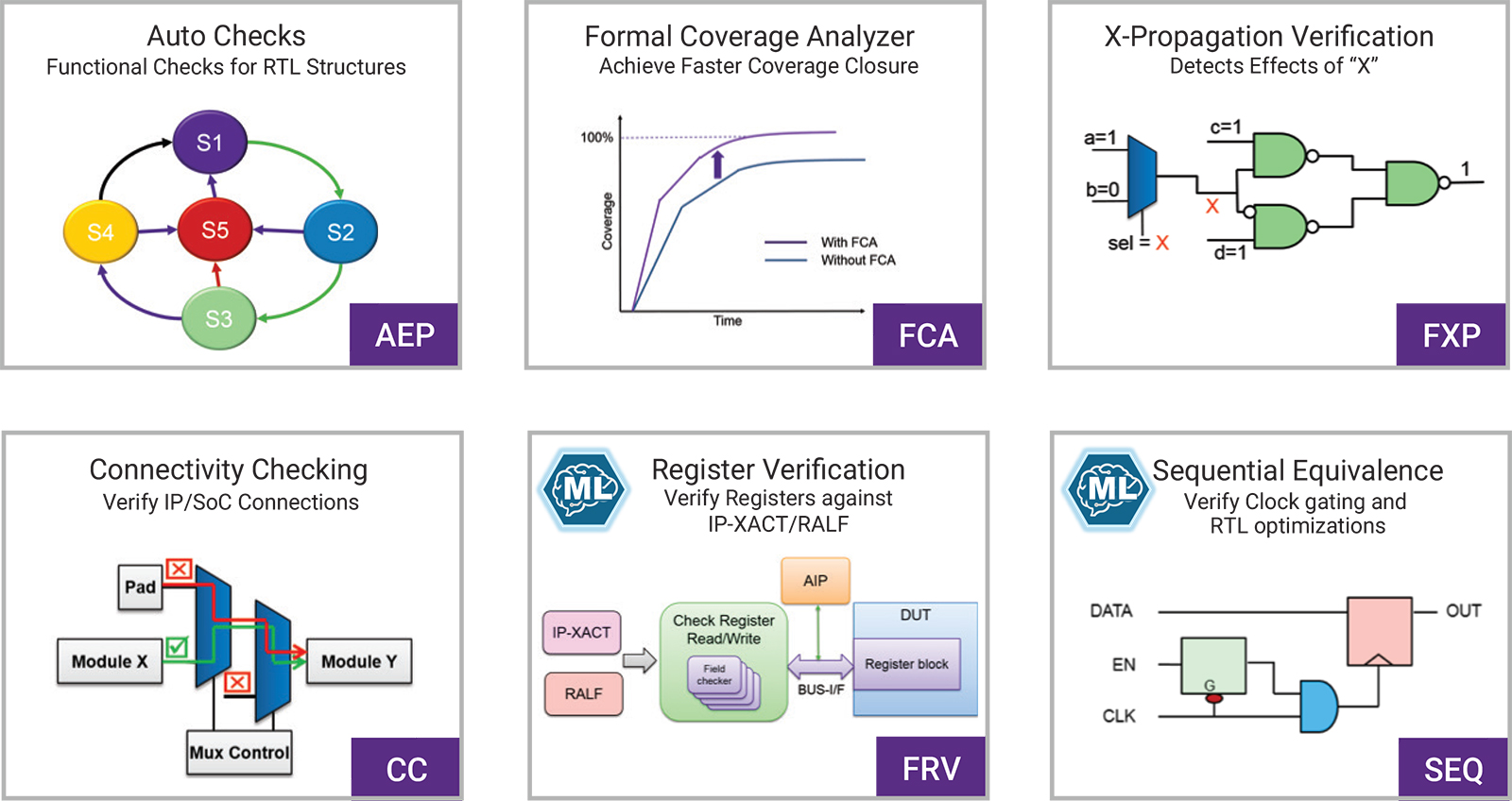

The VC Formal solution includes a comprehensive set of formal applications (Apps), including Formal Property Verification (FPV), Automatic Extracted Properties (AEP), Formal Coverage Analyzer (FCA), Connectivity Checking (CC), Sequential Equivalence Checking (SEQ), Formal Register Verification (FRV), Formal X-Propagation Verification (FXP), Formal Testbench Analyzer (FTA), Regression Mode Accelerator (RMA), Datapath Validation (DPV), Functional Safety (FuSa) and a portfolio of Assertion IPs (AIP) for verification of standard bus protocols.

Productivity Apps

Automatic Extracted Property Checks (AEP)

Automatic functional analysis for out of bound arrays, arithmetic overflow, X-assignments, simultaneous set/reset, full case, parallel case, multi driver/conflicting bus and floating bus checks without the need for dedicated simulation tests.

Formal Coverage Analysis (FCA)

Complementing simulation flows, VC formal provides proof that uncovered points in coverage goals are indeed unreachable, allowing them to be removed from further analysis—saving significant manual effort.

SoC-level Connectivity Checking (CC)

Verification of connectivity at the SoC level. Flexible input format ensures ease of integration. Powerful debugging, including value annotation, schematic viewing, source code browsing and analysis reporting speeds analysis. Automatic root-cause analysis of unconnected connectivity checks saves significant debug time.

Sequential Equivalency Checking (SEQ)

This allows comparison of designs, after register retiming, insertion of clock gating for power optimization or microarchitecture changes.

Formal Register Verification (FRV)

Helps to formally verify behavior of configuration registers for respective attributes like “read only”, “read/write” or “reset value” eliminating the need for directed simulation tests.

Formal X-Propagation Verification (FXP)

Checks for unknown signal value (X) propagation through the design and allows tracing of the failed property to source of X in the Verdi schematic and waveform.

High Value Apps

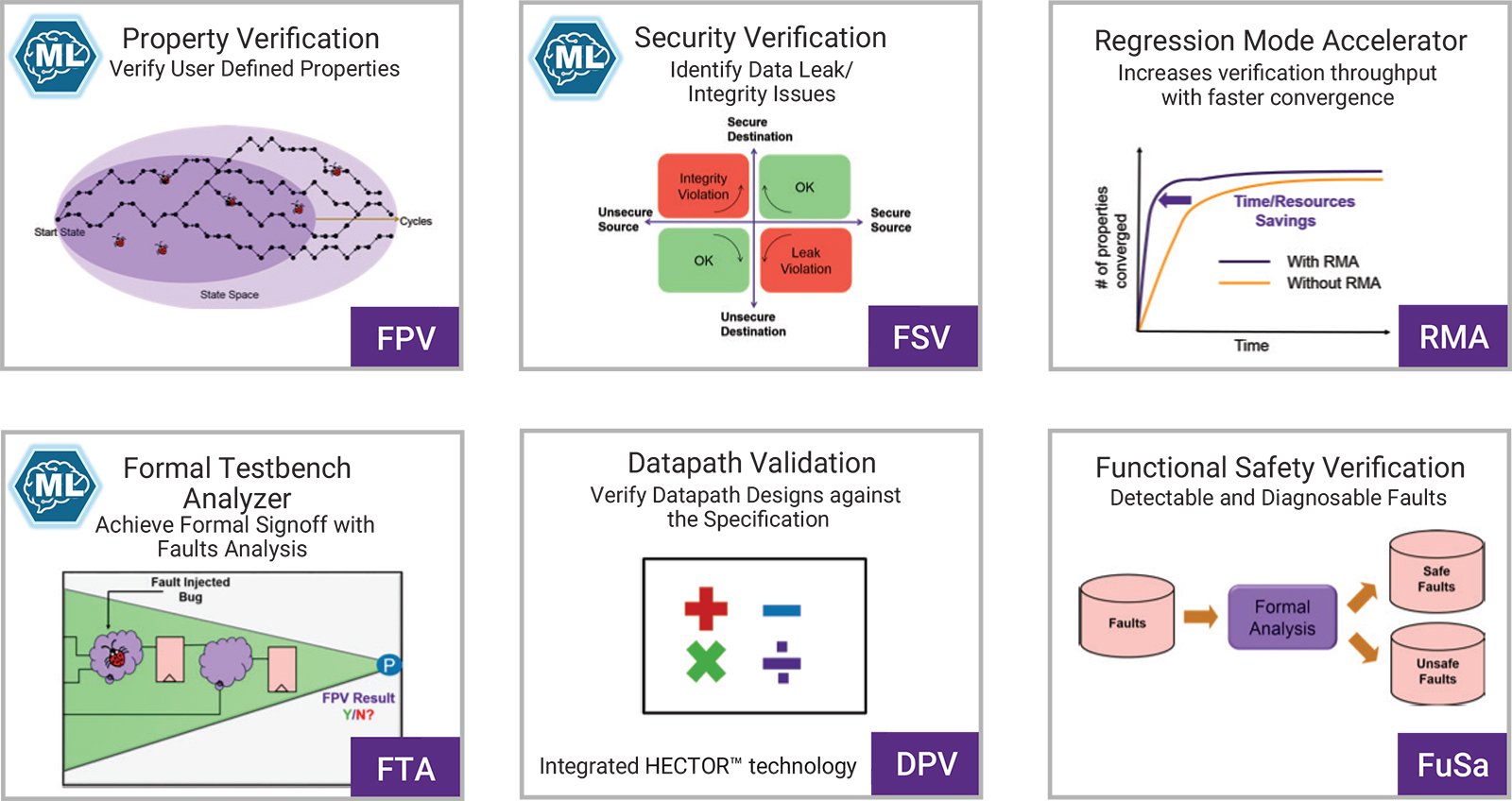

Formal Assertion-Based Property Verification (FPV)

Formal proof-based techniques to verify SystemVerilog Assertion (SVA) properties to ensure correct operation across all possible design activity even before the simulation environment is available. Advanced assertion visualization, property browsing, grouping and filtering allow simple concise access to results. Formal navigator enables debug and "what-if-analysis" with only the RTL design in the Unified Verdi GUI with/without assertions or Testbench.

Formal Testbench Analyzer (FTA)

Certitude™ provides the unique capability to assess the quality of formal environment. The native integration of Certitude with VC Formal provides meaningful property coverage measurements as part of formal signoff and identifies any weaknesses such as missing or incorrect properties or constraints. The native integration delivers 5-10X faster performance compared to stand-alone fault injection methods.

Formal Security Verification (FSV)

Helps formally verify that secure data should not reach non-secure destinations and ensures data integrity, where non-secure data should not over-write (or reach) secure destinations.

Datapath Validation (DPV)

Integrated HECTOR™ technology within VC Formal and contains custom optimizations and engines for datapath verification (ALU, FPU, DSP etc.) using transaction level equivalence. This app leverages the Verdi graphical user interface for debug.

Regression Mode Accelerator (RMA)

Provides significant performance improvement to formal property verification using Machine Learning technology. Use of this app accelerates formal property verification to achieve better convergence of formal proofs for subsequent runs and enables significant saving of compute resources in nightly formal regressions.

Assertion IP (AIP)

High performance and optimized assertion IP for verification of standard bus protocols, and usable in Synopsys VC Formal solution and VCS simulation.

Functional Safety Verification (FuSa)

Functional safety verification is an essential requirement for automotive SoC and IP designs. This App formally identifies and classifies faults based on observability or detectability criteria. Complementing fault simulation with Z01X™, the combined solution reduces the effort and time required to achieve the test coverage closure.

-

VC Formal, https://www.synopsys.com/verification/static-and-formal-verification/vc-formal.html ↩