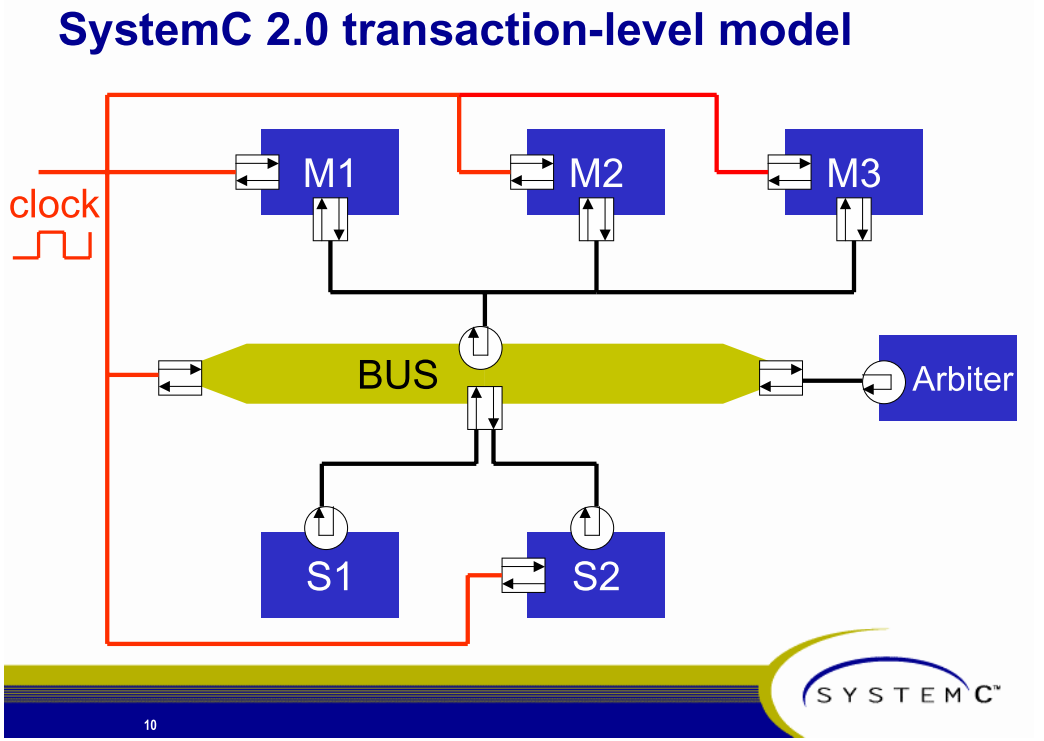

[CodeStudy] The Implementation of TLM Simple Bus in SystemC

The Implementation of TLM Simple Bus in SystemC1

In this project, there are the following c++ files:

simple_bus_main.cpp:simple_bus_test.h: the testbench, descriptions the instance of the modules and the inter connections.simple_bus_master_blocking.h: the blocking master's ports, the constructor as well as private values.simple_bus_master_blocking.cpp: the blocking master's process function.simple_bus_master_non_blocking.h:simple_bus_master_non_blocking.cpp: the process function.simple_bus_master_direct.h:simple_bus_master_direct.cpp: the process function.simple_bus_slow_mem.h: including the implementations of the slave interface.simple_bus_types.h:simple_bus_blocking_if.h: the blocking interfacesimple_bus_direct_if.h: the direct interfacesimple_bus_non_blocking_if.h: the non blocking interfacesimple_bus_request.h:simple_bus_slave_if.h: the slave interfacesimple_bus.h:simple_bus.cpp: including the implementations of master interfaces.simple_bus_fast_mem.h: including the implementations of the slave interface.simple_bus_arbiter.h:simple_bus_arbiter_if.h: the arbiter interfacesimple_bus_arbiter.cpp:simple_bus_types.cpp:simple_bus_tools.cpp:

Implementation of Masters

Implementation of Bus

Dynamic Sensitive

wait(request->transfer_done); // event, dynamic

wait(clock->posedge_event()); // statically sensitive (activated every cycle)

Implementation of Slaves

-

Ric Hilderink, Synopsys, Inc., 2001-10-11 ↩